Original Link: https://www.anandtech.com/show/834

The Future of CPU Packaging: Intel's BBUL

by Anand Lal Shimpi on October 8, 2001 8:30 PM EST- Posted in

- CPUs

It's the people behind the scenes that rarely get the credit they deserve. The people that help put together news broadcasts, movies, and even microprocessors. By far the focus of most discussion about the CPUs we use in our systems is about their silicon; the architecture of the processor, how much cache it has, the bus interface, the clock speed, etc… The only credit we give to the other factors that influence CPU performance and reliability is in our discussions of manufacturing processes. Even then we only talk about how large the die is, how high (or low) yields are expected to be, and what the size of the circuits (manufacturing process) being used. In all of this we actually overlook one of the most important parts of the CPU that is key to stability, performance and the ramping up of clock speeds.

There are two major parts to every CPU, the silicon that actually contains the "processor" and the packaging that connects the core to the rest of the outside world. The packaging of a processor can control how high of a clock speed the CPU will reach, and it can also control factors such as FSB frequencies. How does something as simple as the packaging of a CPU control things like clock speeds? To answer that question we'll have to dive into the world of packaging for a moment.

The Anatomy of a Package

Let's take a look at a present day CPU; for this example we'll use the AMD Duron running at 1GHz.

In the center of the CPU you have what we always refer to as the "core." This is the silicon where it all takes place; all of the calculations, load/store requests, branches, everything happens right here.

In the case of this Duron the silicon is connected to the rest of the chip (known generically as the package) using what is known as a flip-chip package. The reason it is called "flip-chip" is because the exposed part of the core you are looking at is actually the "bottom" of the core; it is flipped so that the core can have direct contact with your heatsink to improve cooling which is vital when looking at the heat production of today's processors.

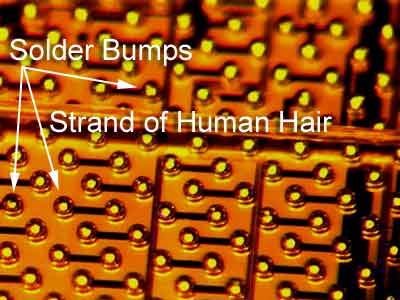

On the other (non-exposed) side of the silicon we actually have the "interface" or interconnect between the silicon and the package. This Duron CPU has 25.18 million transistors in that tiny piece of silicon; groups of those transistors have to be connected to the underside of the package where the pins are located so the CPU can actually communicate with the outside world. The connection between the silicon and the packaging itself is, in this case, made using very small solder bumps that are simply referred to as flip chip bumps. For this particular CPU there are about 3,000 flip chip bumps on the underside of that piece of silicon. For comparison purposes the Pentium 4 has about 5,000 flip chip bumps and the Intel Itanium has around 7,500. As you can probably guess, these solder bumps have to be very small and very carefully placed. As CPUs increase in complexity, the placement of these bumps will become exponentially more difficult. Keep this in mind as we'll come back to this problem later on.

Since all of the processing work gets done on the silicon, the silicon generates quite a bit of heat. If you touch the package of a CPU while it's operational it's not usually hot at all; if you were to stick your finger on the core of a CPU however, you'd quickly be filing a lawsuit against one of our beloved CPU manufacturers. This temperature difference can actually be pretty problematic. As you know, things can expand and contract according to their temperature. So if we have a core running at 50 degrees Celsius and a package that is running at 27, we're going to end up with some problems where the core is expanding at one rate while the package expands at another. If this goes untouched, something is going to crack unless there's a stress reliever.

This is where that bluish/purplish material surrounding the core comes into place. You'll notice that it covers the sides of the core and even seems to extend out past the core. This material is known as the underfill. The underfill acts as a stress reliever and it is present between the silicon and the package, as well as around the base of the silicon-package interconnect to compensate for temperature differences. Since the underfill plays such a key role in connecting the silicon to the package, problems with the underfill can quickly result in defective CPUs. This is one of many cases where you could have a perfectly fine and high yield core, but the packaging holds you back.

The final part of packaging anatomy is the material that the package or substrate is made out of. In the case of the Duron the substrate is ceramic, while in the case of all Intel processors since the P54C (later versions of the Pentium Classic) the substrate is made out of an organic material that's lighter and has other beneficial characteristics which we'll get to later.

Getting the Word Out

When taking you through the anatomy of a processor's package we actually identified a key problem with current packaging methods, a limit on the number of flip chip bumps that can be used to connect the silicon to the substrate. This won't become a limitation that will halt microprocessor production anytime soon, but it will be in a few years. We'll get to solutions to this problem later though.

So now that we know how the data being calculated makes its way from the processor to the substrate (through the use of flip-chip bumps), how does it get from there to the rest of your system? The only way out of the chip is through the hundreds of pins on the bottom of the CPU, but before signals can get to the pins they must travel from the silicon through the packaging.

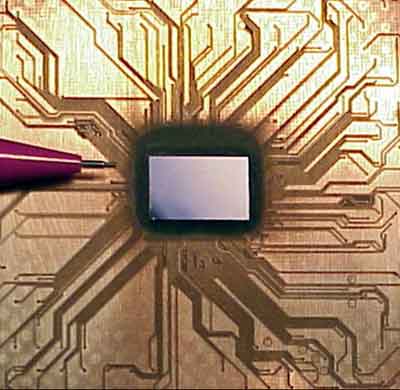

Provided by Intel Corporation

For this example we'll take a FC-PGA (Flip Chip Pin Grid Array) Pentium III processor since you can actually see the lines on the top of the chip. As CPUs become more complex and the silicon decreases in size (smaller manufacturing processes) it's going to become very expensive and very difficult to layout the routing lines coming from the silicon and extending throughout the package.

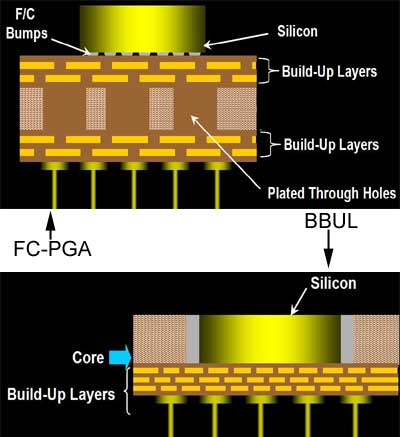

The next limitation is actually on the inside of the package itself; the silicon is on top, and the pins are on the bottom meaning that the signals from the core have to somehow travel through the packaging to get to the pins. If we were to cut through the substrate and magnify the cross-section of the package we'd see a layered diagram much like the picture below.

At the top are the chip attach pads that connect to the solder points on the silicon. At the bottom we have the spaces for pins; and in the middle of this sandwich we have what are known as micro-vias (sometimes just called vias for short). These micro-vias literally connect the top to the bottom of the package. Today's processors are approaching 10,000 micro-vias in their packages; it won't be too long (a few years) before we have 3 - 5x as many micro-vias inside the package.

What does all this mean?

The culmination of all of these limitations and factors to take into account when designing the packaging of a CPU is that new packaging technologies are necessary for tomorrow's CPUs.

Tomorrow's CPUs will be much more complex thus requiring more advanced silicon-substrate interconnect technologies; die sizes will continue to decrease as this happens, creating new routing issues; while all of this is happening CPU clock speeds will increase which requires that even more care be used when designing the entire package.

As clock speeds continue to ramp you can expect to see CPU manufacturers implement advancements in packaging technology. The most recent example of this would be AMD's upcoming Athlon XP CPU which will be AMD's first organic based substrate ever. While Intel has been using organic based substrates for the past few years, AMD has been stuck using ceramic packages for the longest time. The move to an organic based substrate was necessary to allow AMD to ramp to higher clock speeds with their Athlon line of processors.

Although not nearly as high, FSB frequencies are also ramping up as clock frequencies do. Intel's Northwood (0.13-micron Pentium 4) core will eventually use a 533MHz FSB, Intel's Prescott core will use a 800MHz FSB, and their Tejas core will use an incredible 1.2GHz FSB upon its release.

AMD isn't sitting still either; their Hammer line of processors is rumored to have an 800MHz FSB as well. It wouldn't be too shocking if part of the reason for introducing an organic based substrate was to get all of the kinks worked out for a debut on their Hammer processors.

If you remember the early rumors about the desktop Palomino having problems working at the 133MHz FSB, these early issues were most likely packaging related as AMD's manufacturing line adjusted to the new organic packaging.

I've got the power

You've all heard the expression "computers count in 1s and 0s" but your CPU doesn't sit there and count beans all day. Instead it looks at the voltage output of various combinations of transistors and determines whether the output is a 1 or a 0 depending on the value of the voltage (high or low, 5V or 0V, etc…).

Now look at what has happened to CPU voltages over time. The original Pentium 60/66MHz processors ran off of a 5V core voltage and today's CPUs are down to 1.75V and lower. This constant reduction in voltages is making the difference between a "high" voltage signal and a "low" voltage signal very small; this also makes it easy for a low voltage signal plus some noise to be thought of as a high voltage signal, effectively making a 1 out of a 0. This can lead to instability and inaccuracy in calculations so there must be a way around it.

The way to fix this is simple; add capacitors to filter out the noise. The problem with that "simple" solution is that the capacitors have to be placed very close to the core of the CPU and the proximity of the capacitors to the CPU core is governed by, you guessed it, packaging technologies. This is why you see capacitors on the underside of the Pentium 4 CPU as they are as close to the core as possible.

Bumpless Build-Up Layer: The Future of Packaging

While AMD has taken the performance crown from Intel on numerous occasions, AMD cannot compete with Intel's manufacturing capabilities. Intel actually has a branch whose sole purpose is to deal with packaging and the needs of tomorrow's processors. Intel has been talking about 1 billion transistors in a chip running at 10GHz+, so it's no surprise that they have 900 people working on packaging technologies.

Intel's Assembly Technology Development team is 900 people strong with most of them located in Arizona. And it is out of Arizona that today's announcement on a breakthrough in packaging technology is made.

Although the technology won't be put to use for another 5 or 6 years, Intel's Bumpless Build-Up Layer (BBUL) will definitely change the face of packaging. The beauty of BBUL is that the silicon is actually integrated into the die. A BBUL CPU will be manufactured by building the package one layer at a time and embedding the silicon into the package after testing. Remember the issue of the flip-chip solder bump density? That is no longer an issue with BBUL since there are no more solder bumps; the silicon is directly embedded in the package. Another benefit of this is that since the core is no longer raised, there is no potential for any chipped/cracked cores due to improperly installed heatsinks. Intel did mention however that they would probably still use heatspreaders with this technology meaning that you wouldn't be able to chip/crack the cores in any case.

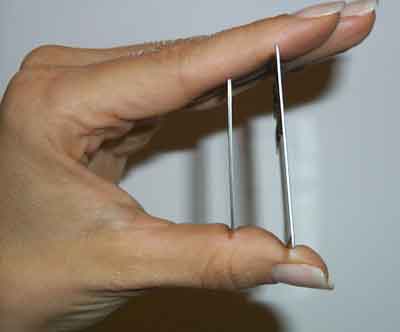

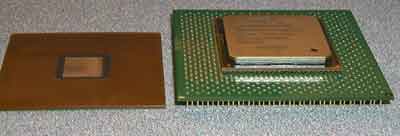

This also brings the silicon closer to the capacitors on the bottom of the CPU, increasing power delivery efficiency as we mentioned earlier. The package is also physically thinner, and as you can see from the following pictures it is a lot thinner (note: the prototype BBUL chip used a core approximately the size of Intel's 0.13-micron Northwood core and didn't have any pins attached to it. The final chips will obviously have pins. All photos were courtesy of Intel Corporation).

Left: BBUL Prototype Chip, Right: A Credit Card

Left: Pentium 4 Chip, Right: BBUL Prototype Chip

The benefits of this type of packaging can also be extended to multi-core CPUs. One of the major problems with outfitting a CPU with two cores is that the two must be tested together in the final CPU and if just one is bad, the entire CPU must be thrown away (AMD's SledgeHammer will unfortunately face this problem it seems). With BBUL you'll be able to embed two CPU cores using two separate dies and connect them with an internal high-speed bus, giving you the benefits of a multi-core CPU but also allowing you to test the cores individually before packaging them into a single CPU.

Final Words

We don't normally get the chance to present articles like this to you, but we hope you enjoyed the content. Intel's BBUL is definitely a step forward in CPU packaging technologies and it will be useful to all manufacturers since the technology can be used to package chipsets, integrate higher performance graphics cores in North bridges, and even offer very high performance L3 cache integrated into a multi-chip processor module.