Original Link: https://www.anandtech.com/show/2091

IDF Fall 2006 - Day 2: Geneseo, Santa Rosa, Memory Roadmap and More

by Anand Lal Shimpi on September 28, 2006 3:43 AM EST- Posted in

- Trade Shows

Earlier today during Pat Gelsinger's Keynote, Intel announced its work with IBM to develop the successor to PCI Express, codenamed Geneseo. We likened Geneseo to AMD's Torrenza initiative, and were able to get some more background information on Geneseo and how it is likely to be implemented once it makes its debut.

Intel is in a precarious situation; since there is a demand for a higher bandwidth, lower latency interconnect than PCI Express, AMD's Torrenza platform makes a lot of sense for 3rd party solution and accelerator vendors. Those vendors would be able to gain access to a high bandwidth, low latency interconnect by utilizing coherent Hyper Transport and plugging directly into an Opteron socket or via HTX slots on a motherboard. With no competing standard from Intel and AMD being an easy company to work with, momentum for AMD's Torrenza platform was growing in anticipation of its eventual implementation.

AMD's Torrenza Platform

From Intel's standpoint, simply releasing a competitor to Hyper Transport wouldn't make a lot of sense since it would simply further divide the market. Instead, Intel and IBM got together and proposed an extension to PCI Express that would offer both higher bandwidth and lower latency. Since PCI Express is already an industry standard embraced by all sorts of manufacturers, the evolutionary move to another PCI Express based interface makes a lot of sense and is more likely to gain traction than requiring vendors to produce HTX compatible solutions.

Although the spec is not yet defined, Geneseo (pronounced jen-eh-see-oh) PCI Express will be a backwards/forwards compatible interface, simplifying migration. Transfer rates will be on par with PCI Express 2.0, at 5 GT/s per lane, doubling the bandwidth of current PCI Express.

Geneseo is designed to tackle all of the sorts of add in "accelerators", whether they are GPU or physics, as long as they don't need cache coherent communication with the host CPU. If they do need full cache coherency, then Geneseo falls short however Intel's announcement that it would be offering FSB bus licenses to companies like Xilinx that are interested in a cache coherent interface picks up where Geneseo left off.

Basically Intel's interconnect solution is two fold:

1) If you don't need a cache coherent interface, then Geneseo will work just fine. It will be an industry standard specification, built upon PCI Express that will undoubtedly have broad industry support much like PCI Express does today.

2) If you do need a cache coherent interface, for example if you're building an accelerator that does need to work very closely with the CPU, then you'll have to license Intel's FSB for use in Intel systems, or design a coherent Hyper Transport interface for use in AMD systems.

More than likely what will happen is that once Geneseo gains traction the majority of accelerators, those that don't need to remain near the CPU, will transition to a Geneseo interface since you only need to build one accelerator that can work on both AMD and Intel platforms (assuming AMD offers Geneseo support, which since it supports PCIe we can't see AMD not supporting Geneseo). In the cases where you're building an accelerator that must reside next to the processor, then you'll have to build a platform specific device, e.g. something that implements Hyper Transport for AMD or something that utilizes Intel's FSB license for Intel platforms.

Assuming that the eventual specifications of Geneseo are competitive with what AMD can offer with HTX slots in its Torrenza platform, then we do see a lot of promise with Geneseo. We would still like to see Intel ditch its aging FSB architecture, but it appears that the process of following in AMD's footsteps is a slow one.

Santa Rosa Arrives

Intel just recently launched its mobile Core 2 Duo platform, built around the Merom core but using the same 945 Express chipset family that was introduced alongside the Core Duo processors. By keeping the platform the same, Intel ensured a far more seamless transition to the new processors (and kept OEMs somewhat happier) than had it introduced a new chipset and processor at the same time. In Q1 of next year however, Intel will be updating its Centrino platform to catch up to the innovation that was introduced with Core 2 Duo. We've talked about the new platform in the past and it's known by the code name Santa Rosa.

Santa Rosa block diagram

On the processor side, 65nm Merom based Core 2 Duo processors will still be at the heart of Santa Rosa. The difference this time around is that Intel will introduce 800MHz FSB Core 2 Duo processors, compared to the 667MHz Core 2 Duo processors that were just launched.

Along with the faster FSB, Intel will for the first time add an adjustable FSB clock frequency to help reduce power. Currently, on battery power, Core 2 Duo based notebooks will operate in a low frequency mode (LFM) at a low voltage. However, this LFM still runs with the FSB clocked at full speed, which is 667MHz in the case of current Core 2 Duo notebooks. With Santa Rosa, Intel is introducing a super low frequency mode (super LFM) that underclocks the FSB from 800MHz to 400MHz, also cutting the CPU speed in half, down to 600MHz from 1.2GHz at its LFM state. With a slower FSB frequency and lower CPU clock speed, Santa Rosa hopes to save more power when idle than its predecessor.

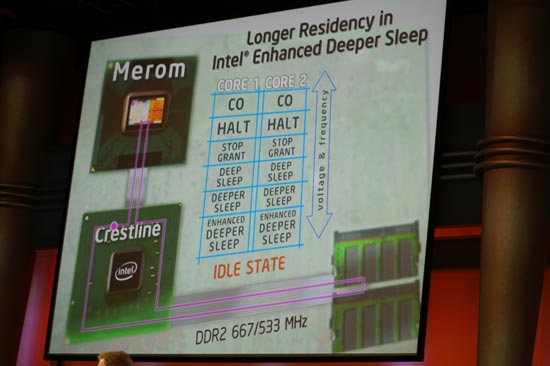

Of course the chipset in Santa Rosa is Intel's mobile 965 solution, codenamed Crestline. In addition to supporting the faster 800MHz FSB, there is one important power saving feature that was added to the chipset. In the Core 2 Duo's lowest power state, often referred to as Enhanced Deeper Sleep, all data in its cache is flushed to main memory and the cache is powered down to conserve battery life. In the current Core 2 Duo platform, if the memory controller is still handling memory requests, it will continually wake the processor up looking for data in its cache, even though the cache is empty.

The new 965 chipset goes through a handshaking process with the CPU so it knows when the Core 2 processor's cache has been flushed, thus knowing not to wake it up until it absolutely needs to. It sounds like a simple fix but it should result in reduced power consumption.

Along with the new chipset comes an updated integrated graphics core, which we have been testing in our labs on the desktop side. Intel insists that the new integrated graphics offers similar average power to the 945G graphics, but under load we're expecting it to consume more as it is a full DX9/PS3.0 part.

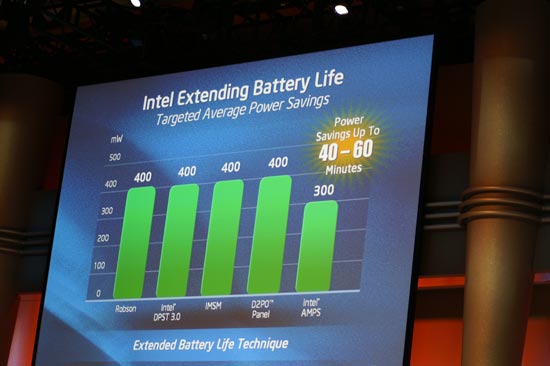

Those are all of the major changes to the chipset, but there are other improvements to the platform that will be joining us with Santa Rosa. Intel's Dadi Perlmutter, Senior VP and General Manager of Intel's Mobility Group gave us an interesting tidbit of information; he stated that for every 1W of average power you can reduce on a notebook, you gain 20 - 30 minutes of battery life. With that in mind, he threw up this slide showcasing all of the areas that Intel is looking to save power in:

We talked about Robson technology yesterday, and it will surely reduce some power consumption by keeping the hard disk spun down as much as possible, but an interesting technology is Toshiba/Matsushita's interlaced display offering. The technology demonstrated is quite simple; when running on battery power, if the display detects that no motion video is being played back, it will function in an interlaced mode (displaying only half the vertical resolution at any given time) to conserve power.

Dadi's demo showed a savings of over 200mW when operating in interlaced mode, and suggesting a savings of close to 400mW for higher resolution and brighter panels than the one being demonstrated.

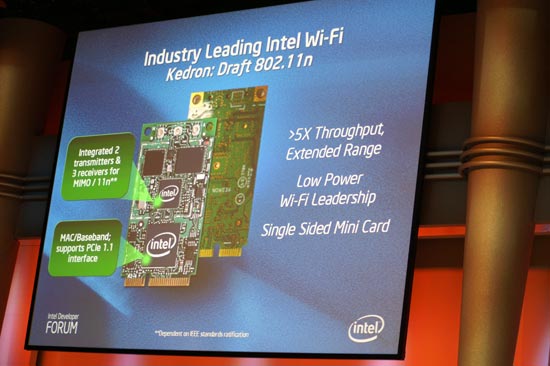

The final discussion of Santa Rosa centered around wireless technologies. A requisite part of Santa Rosa will be Intel's Kedron 802.11n wireless solution, which for the first time in Intel history will be a Centrino bundled wireless solution released before a finalized IEEE spec. The Kedron 802.11n wireless will use the Draft-N spec and Intel assures us that its solution will be significantly better both in performance and interoperability than current Draft-N solutions. We will have to wait and see, but it would be quite surprising for Intel to compromise the quality associated with its Centrino brand by bundling a poor wireless solution; we have high expectations for Kedron and Intel seems confident it can deliver in Q1 of next year.

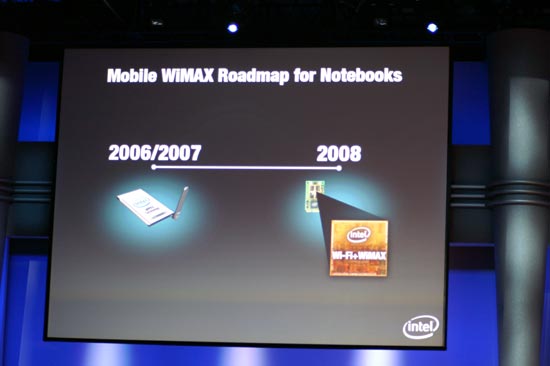

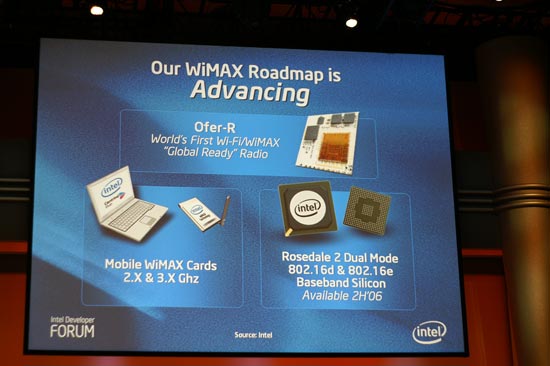

While WiMAX isn't a part of the component list necessary for Centrino certification, Intel will begin offering WiMAX cards for notebooks in 2006/2007; by 2008 you can expect WiMAX integration on the motherboard level.

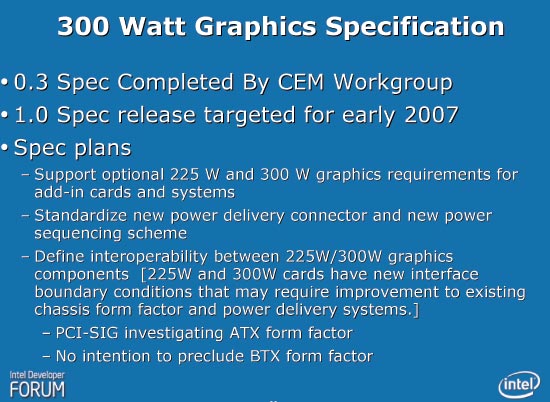

Brief Mention of 300W Graphics

It looks like there are going to be two high end GPU specs for power, with a 225W and a 300W spec. We mentioned during Computex that we're expecting the upcoming DX10 GPUs from ATI and NVIDIA to begin pushing the power envelopes much higher than we've seen in the past, and the fact that we're seeing discussion of specs for 225W and 300W GPUs means that we should probably expect even higher power consumption cards from graphics vendors.

Intel Does Graphics

Intel was cautiously quiet on the subject of its own entry into the discrete graphics market. Although ATI is convinced that Intel will make a significant entry into the graphics market in the next two years, Intel isn't saying anything at all.

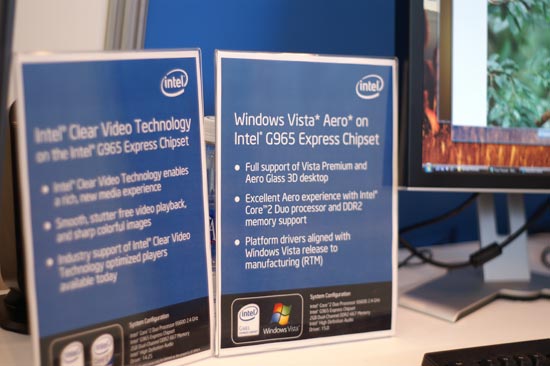

Intel's new integrated graphics running Vista with Aero enabled

We are looking at Intel's latest G965 graphics solution, which is a significant departure from Intel integrated graphics offerings of previous chipsets in terms of being a more modern architecture. We are working out some driver issues with Intel currently and hope to be able to provide at least a first look at the new integrated graphics core in the coming weeks.

Intel's G965 integrated graphics running the HQV video quality benchmark

While Intel wouldn't confirm plans to produce higher end graphics cores, its representatives did confirm that we would see further segmentation in the integrated market. Currently Intel is offering two versions of its integrated graphics, a slower version found in the Q965 chipset and a faster version in the G965. Within the next 12 months you can expect Intel's integrated graphics to segment more dramatically. At the very low end you can imagine a corporate desktop integrated graphics solution that can basically offer video decode acceleration and support for Vista's Aero Glass UI, but a terrible performer in games. Then, in the mid range, you'd have today's G965 graphics offering and to round things off Intel would create an even higher end integrated graphics solution to offer better performance for entry-level gamers. In the past, our expectations for a minimum level of gaming performance and Intel's have not lined up even in the least, but we're hoping with this and the next generation of Intel integrated graphics that we'll see more of what we've been asking for, for years.

Whether or not Intel will make an entry into the discrete GPU market has yet to be seen, but one thing is for sure - Intel is definitely taking its graphics cores more seriously.

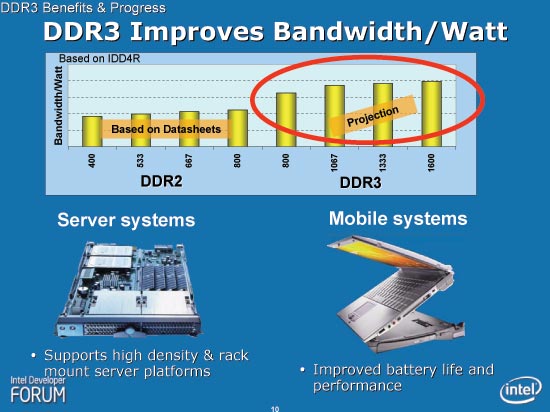

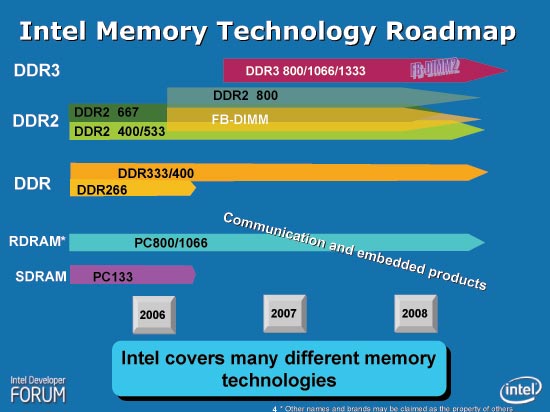

Intel's Memory Roadmap

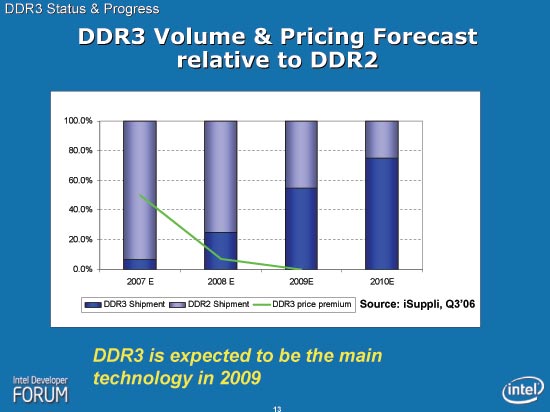

Yesterday we saw some early demonstrations of DDR3-1066 on Intel desktop platforms. DDR3 will be introduced with the new Bearlake family of chipsets in 2007, and will begin a slow and steady ramp much like DDR2 did on 915.

At launch, Intel is forecasting a 60% price premium for DDR3 over DDR2, but by the end of 2008 is expecting that premium to drop to below 10%. Although the transition is starting in 2007, DDR3 won't become mainstream until 2009 based on the data Intel shared with us.

Without being able to look at AMD's memory roadmap, it's difficult to say whether or not we will have a dual-technology memory market again with the transition to DDR3. Chances are that AMD will choose to stay with DDR2 until 2008 at the earliest, especially given DDR3's price premium in 2007. AMD has always been more practical/user focused with its technology decisions, while Intel tends to focus on the long term and driving the industry towards new technologies. We need both approaches to keep prices low and to actually move technology forward, although it can seem frustrating at times.

With regards to FB-DIMMs, Intel was quick to shoot down reports of the technology's early demise. The second version of FB-DIMM will be available alongside DDR3 memories and Intel will continue to use the technology until 2009 at the earliest. Intel's memory roadmap after 2009 is unclear, but FB-DIMMs will be used for at least that long - still only in the high end workstation/server markets.

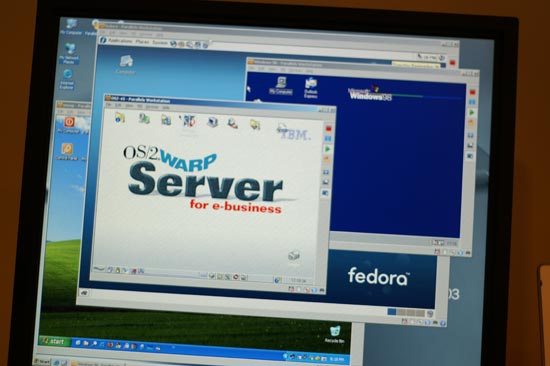

Parallels at IDF

It's still very odd seeing Macs at an Intel Developer Forum; every time we pass one we get this feeling that someone must have snuck one in to a demo, before it eventually sinks in that we're staring at an Intel based Mac.

Windows Vista running under OS X on a MacBook Pro

Parallels, the developers of the Parallels Desktop for Mac VM manager, was at Intel's Technology Showcase demonstrating its VM software with VT support.

While the demonstrations were nothing new, the Parallels representative did say that in the next week we should expect an updated build of Parallels Desktop for Mac with support for PAE. PAE support is critical because currently, you can't run 32-bit Windows XP under Parallels on a Mac Pro outfitted with more than 3.5GB of memory. The only option is to either remove some of your memory or disable it in software, which also means you are running with less memory under OS X. Once PAE support is enabled, Windows XP running under Parallels on OS X will be able to work just fine with Mac Pro configurations equipped with more than 3.5GB of memory.

Also, by the end of this year, we should expect a further update of Parallels Desktop with some level of hardware 3D acceleration support. The Parallels rep indicated that it would be sufficient for games but we remain skeptical until we can see it in action.

Parallels also makes VM managers for Windows and Linux

Final Words

This year's Fall IDF is almost over, but we've still got some miscellaneous content remaining and a half day of information and presentations. If it's worth reporting, you'll know where to find it.