Original Link: https://www.anandtech.com/show/2089

IDF Fall 2006 - Day 2: Opteron vs. Xeon, SSE4 & Intel's Torrenza competitor Announced

by Anand Shimpi & Virginia Lee on September 27, 2006 1:12 PM EST- Posted in

- Trade Shows

Back when Pat Gelsinger was Intel's CTO, he was on stage at these IDF Keynotes talking pure, unadulterated technology and research - much like Justin Rattner was doing yesterday. Pat is an absolutely excellent presenter, arguably Intel's best; unfortunately, these days he spends his time talking about the Enterprise market - and historically, the Enterprise keynote has always been the least interesting keynote of IDF. Against all odds, Pat managed to make the latter half of the keynote interesting with some important announcements that we'll talk about in the coming pages.

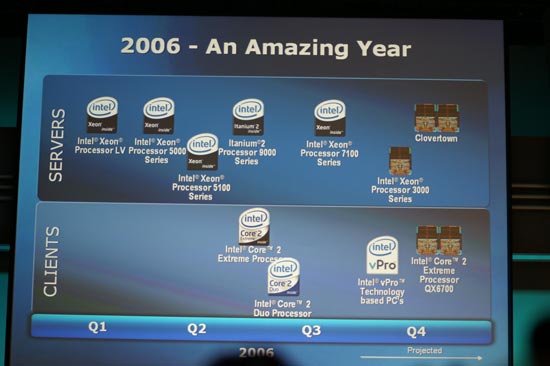

Gelsinger's keynote started with a recap of what's been released in the past six months: mainly Core 2 based processors into the server and client markets.

Given that this is the first IDF since the launch of Intel's Core 2 based processors, it's not surprising that the majority of the show has been touting the performance advantages of Intel's existing Core 2 products rather than new products.

![]()

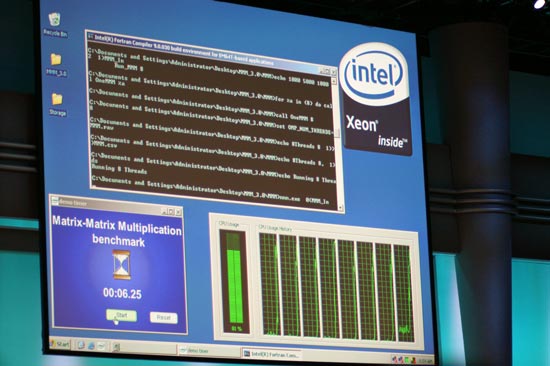

Ever since Core 2 launched, Intel has been unusually competitive in that it has done an unprecedented amount of public Intel vs. AMD benchmarking. From setting up an AMD system to compare to Conroe at last IDF to having a live Socket-F Opteron performance comparison today, Intel is proud of its performance advantages and is not shy of talking about them.

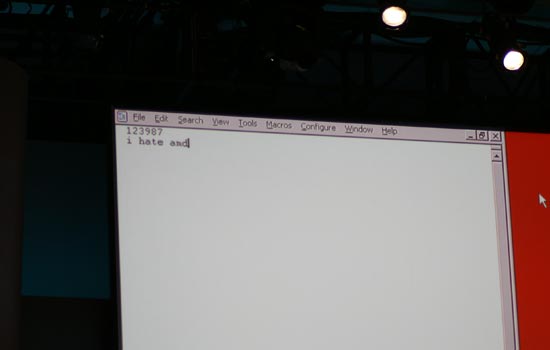

The second line is Pat Gelsinger's password captured by an Intel rep playing a hacker during a security demo at today's keynote

The Socket-F Opteron 2.8GHz vs. Xeon 5160 (3.0GHz) demo was a simple performance test using a Matrix-Matrix Multiplication benchmark (sounds a lot like Linpack). Obviously the Opteron system lost taking 67.49 seconds to complete the benchmark compared to 39.06 seconds for the Xeon 5160 system (both systems were dual socket). Power consumption was lower on the Xeon system at 370W vs. 444W. Without knowing the configurations of both systems (other than Intel saying that they were as close to identical as possible), we can't really say much about how comparable these results are.

Gelsinger then "challenged" his demo assistant to upgrade the Xeon box to new Clovertown based, quad-core Xeon processors within the next 8 minutes.

The demo assistant simply swapped out the old Xeon 5160s with new Low Voltage Clovertown based Xeons running at a clock speed almost 900MHz lower than the 5160s (around 2.1GHz). Despite the lower clock speed, having twice as many cores in the system let the new LV quad-core Xeon setup complete the benchmark in 31.01 seconds, and at marginally higher power consumption of 380W.

Intel Announces new Instructions for 45nm, SSE4 and more

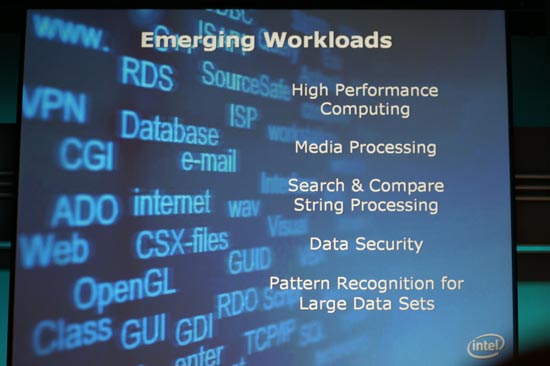

Unexpectedly, Gelsinger announced the 50 new instructions that will be present in its upcoming 45nm processors (Penryn and Nehalem) - it's "SSE4 and more".

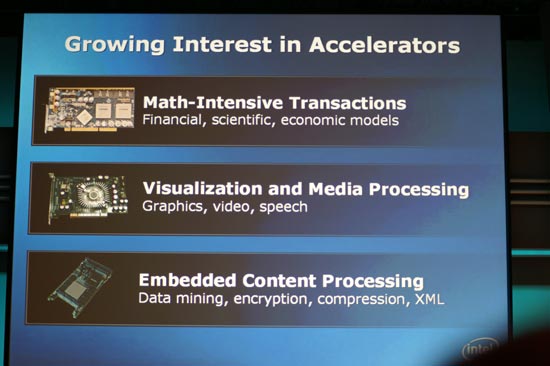

These are some of the workloads the new instructions will help accelerate

Today Intel will be publishing a white paper detailing the new instructions and as they get implemented in silicon, Intel will disclose more information about the instructions.

Intel's approach to SSE4 disclosure is a significant departure from how previous x86 instruction extensions have been disclosed by the company. It's another example of Intel's more open and friendly approach to its upcoming roadmaps; we're hoping Intel will only continue to be more open with its future plans, and we do have AMD to thank for keeping the pressure on Intel to bring about such a dramatic change in behavior.

Intel Follows AMD's Lead, Again: Cloning Torrenza

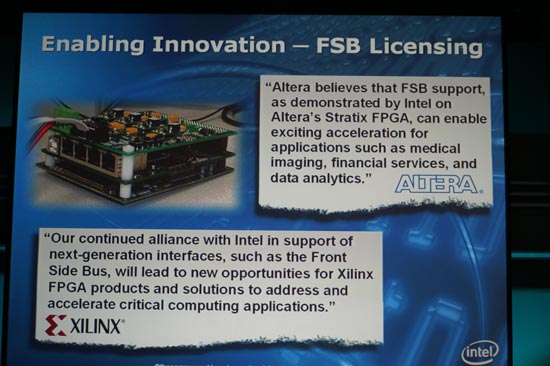

In another example of a string of Intel following AMD's lead, Gelsinger announced extending Intel's FSB license to FPGA manufacturers like Xilinx so that companies can produce other chips that can work alongside Intel processors with a direct FSB connection to the MCH. This should sound a lot like a less elegant implementation of AMD's Torrenza initiative; as you may remember, Torrenza is the platform standard that AMD introduced to allow other, non-AMD processors (or accelerators) to be installed in standard Opteron sockets through licensing and use of the coherent Hyper Transport specification. Intel's FSB licensing will also allow various accelerators to be plugged into a high bandwidth, low latency (potentially cache coherent) bus that would connect directly to the MCH in an Intel system.

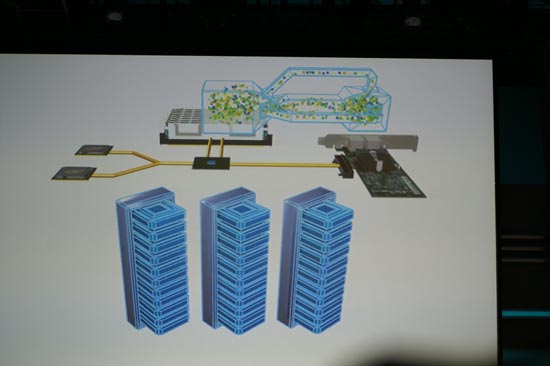

This device somehow implements Intel's FSB license

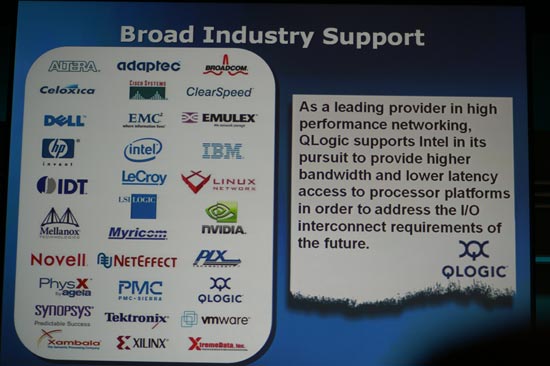

Intel also announced work with IBM to create an extension to PCI Express, codenamed Geneseo that would be used as a higher bandwidth, lower latency interface for everything from graphics cards to physics accelerators. Gelsinger threw up a slide that showcased the broad industry support for creating products that would work with the Geneseo interface. Notable members of the alliance are NVIDIA and AGEIA for its PhysX card, indicating that Intel's thinking is similar to AMD's in that there could be a future for physics accelerator cards or even a higher speed, lower latency interconnect for GPUs that would utilize this interface. Note the absence of ATI from the list of partners supporting Intel's efforts.

Effectively, what Intel is hoping to do is gain momentum and industry support for an alternative to AMD's Hyper Transport for use with various 3rd party accelerator cards. Since Intel is unlikely to embrace Hyper Transport and AMD's Torrenza's initiative, simply extending PCI Express with additional focus on creating a higher bandwidth, lower latency version of the bus for these accelerator cards with the help of the rest of the industry (except AMD) is the next best option.

Intel expects to iron out a specification in the next 1 - 1.5 years, and the first products will be available in the coming years after that. Obviously, AMD has a much larger head start in this area and we're interested to see how things pan out given AMD's timing advantage and industry support for Hyper Transport.

IBM came on stage to talk about some of the things Intel and IBM focused on in developing the spec for the new Geneseo interface spec for 3rd party accelerators to communicate directly with the MCH in a system. The information that was shared was vague at best, but the animations during the presentation give you an example of a usage model Intel is looking at with its Torrenza-like platform approach.

Based on the vague comments by IBM, it looks like these accelerators running over the Geneseo interface could be cache coherent, support reordering of memory requests in order to prioritize the most important requests and able to be power managed must like any other component in the system.

An Energy Efficiency Benchmark & Final Words

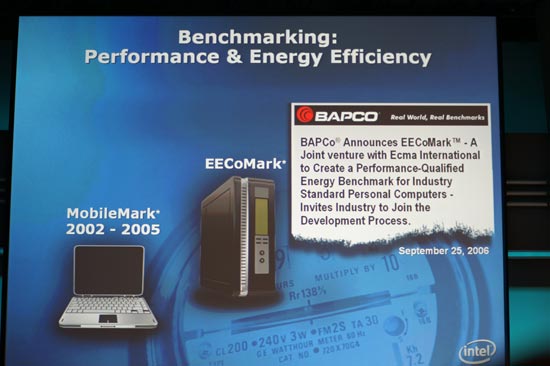

Gelsinger also announced that BAPCo would be working on a desktop client energy efficiency benchmark, sort of like a MobileMark for desktops, called EECoMark. The announcement was the only information we got, with no idea of release date or any other details about the benchmark.

We're particularly interested in it as it would provide a more standardized approach to testing performance per watt than what we do today.

Final Words

Today is a busy day with three keynotes planned and of course we'll be bringing you coverage of all of them. But the two major announcements from Gelsinger's opening keynote, SSE4 and Intel's more open FSB licensing, should be enough to think about for the time being.