Original Link: https://www.anandtech.com/show/13242/hot-chips-2018-intel-on-graphics-live-blog

Hot Chips 2018: Intel on Graphics Live Blog (11:30am PT, 6:30pm UTC)

by Ian Cutress on August 20, 2018 2:25 PM EST- Posted in

- CPUs

- Intel

- Radeon

- Hot Chips

- GPUs

- Trade Shows

- Live Blog

- Vega

- RX Vega

- Kaby Lake-G

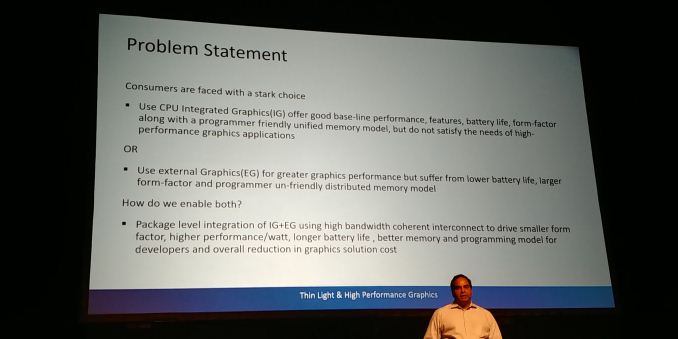

02:21PM EDT - Intel is talking graphics! We're expecting a lot of discussion about Kaby Lake G, with Radeon graphics, however the slide deck is going to talk a lot about power distribution methods in order to support the chip.

02:24PM EDT - Should start in a few minutes

02:30PM EDT - Presenter has worked on AES-NI and SSSE3

02:31PM EDT - Lead architect of Kaby G

02:31PM EDT - One of the most interesting products at Intel

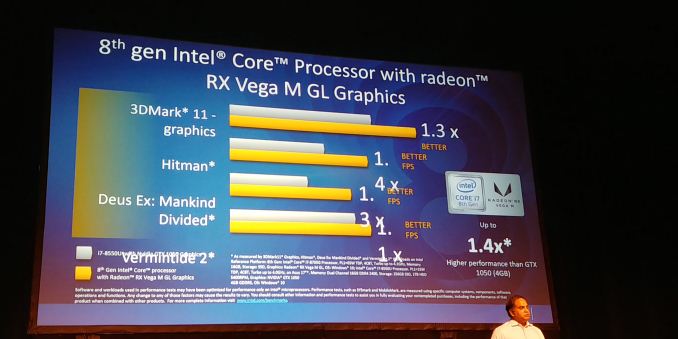

02:32PM EDT - Combine high-end gaming with thin and light devices

02:32PM EDT - Aim to bridge the divide between thin and light and DTR

02:32PM EDT - A multi-generational project (!) (!)

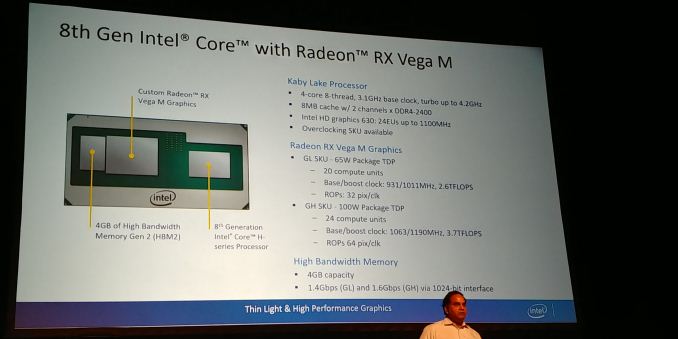

02:33PM EDT - Kaby Lake-G

02:33PM EDT - About using multiple chips for an innovative product

02:33PM EDT - Kaby Lake processor, Radeon graphics, HBM2

02:34PM EDT - There's a framed version of the agreement with AMD at HQ

02:34PM EDT - HBM2 was customized to Intel's needs

02:34PM EDT - Enable VR in mobile form factor

02:34PM EDT - Mobile form factor meant no GDDR

02:35PM EDT - First high-volume mobile part with HBM

02:35PM EDT - 9 Displays

02:35PM EDT - NUC can access all these displays

02:36PM EDT - 'How did we make this happen'

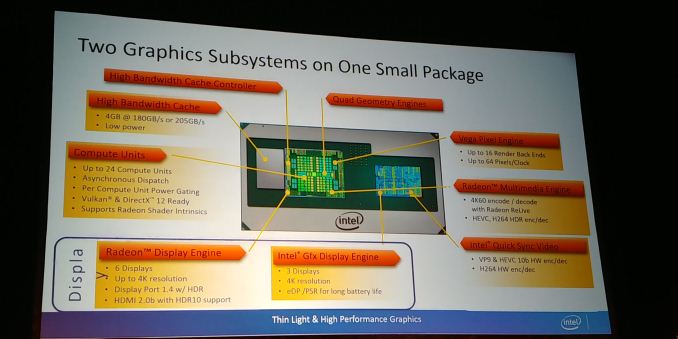

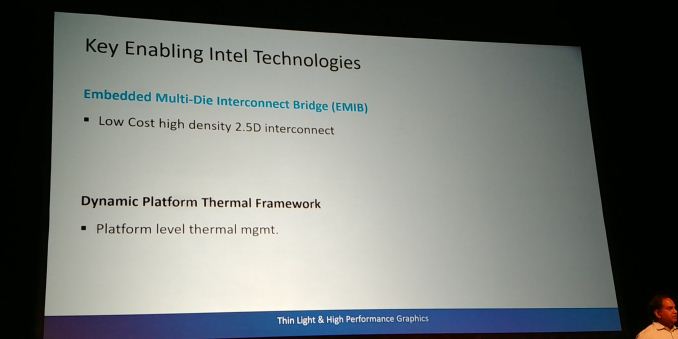

02:36PM EDT - EMIB and DPTF

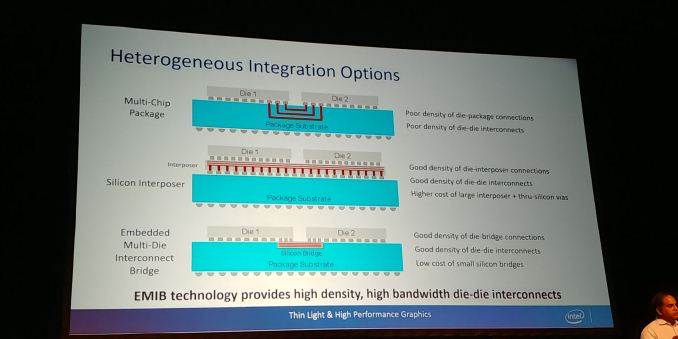

02:36PM EDT - Integration options

02:36PM EDT - MCP, Interposer, or EMIB

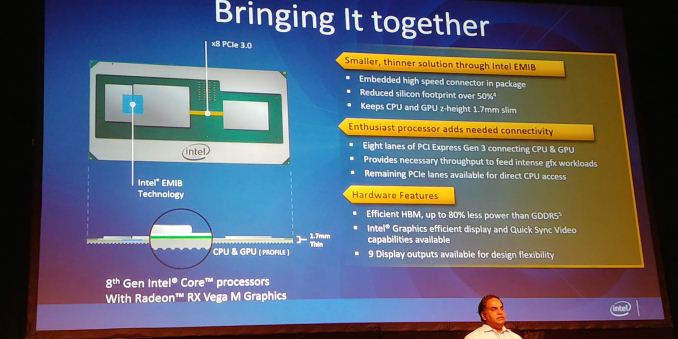

02:37PM EDT - Intel uses MCP for CPU to GPU, and EMIB for GPU to HBM

02:38PM EDT - For non-high density connectivity, use package. For density, use EMIB

02:38PM EDT - Large number of wires and data in low power with EMIB

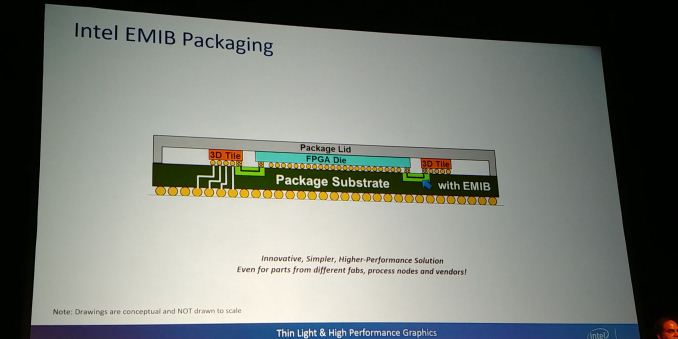

02:39PM EDT - EMIB allows different geometries, different manufacturers, all in one package

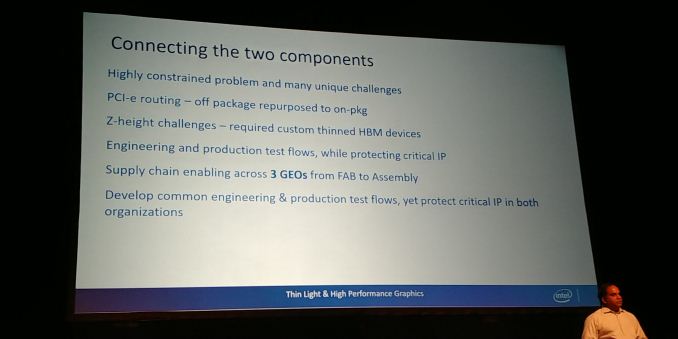

02:39PM EDT - Several constraints

02:39PM EDT - Taking off-the-shelf components (minimal changes)

02:39PM EDT - Connections had to be PCIe

02:39PM EDT - in discrete form

02:40PM EDT - Normally routing length for PCIe is 8-inches

02:40PM EDT - Did a lot of simulation on 2 inches

02:40PM EDT - z-height challenges

02:40PM EDT - for heatsink

02:40PM EDT - HBM2 at 700 microns, taller than the other components

02:40PM EDT - had to be thinned in a custom manner for Intel

02:41PM EDT - Independent testing and then assembly

02:41PM EDT - 'Logistical Nightmare'

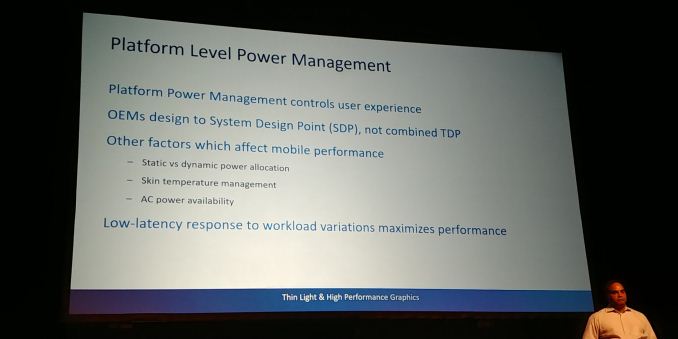

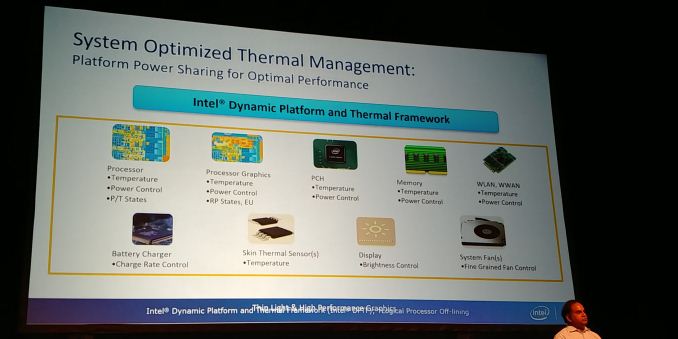

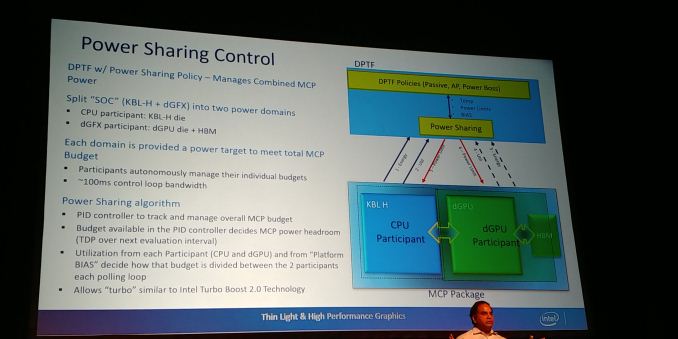

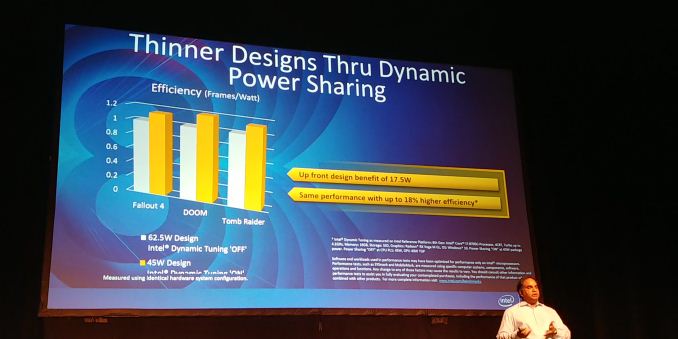

02:41PM EDT - Now Dynamic Platform Thermal Framework

02:42PM EDT - Power management controls UX

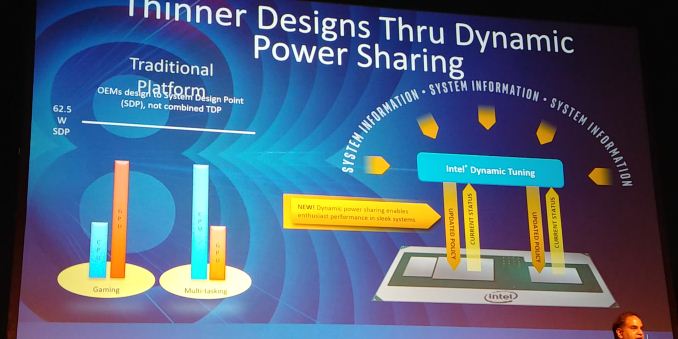

02:42PM EDT - OEMs design to SDP, not combined TDP

02:42PM EDT - Maximising perf while minimizing thermal issues

02:43PM EDT - Low latency too

02:43PM EDT - Everything is controlled to minimize power where it is not needed

02:43PM EDT - Keep power at peak given thermal contraints

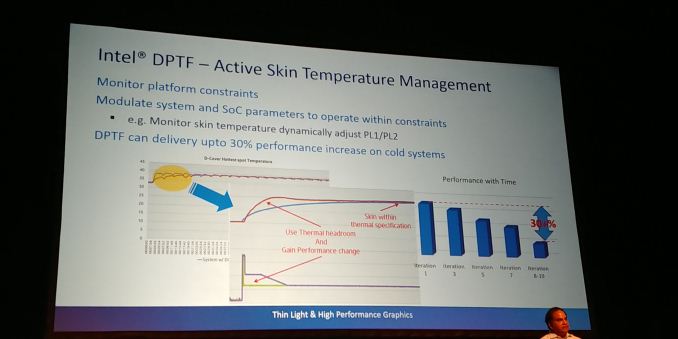

02:44PM EDT - Depending on the starting thermals, more performance based on turbo

02:44PM EDT - Take advantage based on thermal characteristics

02:44PM EDT - Make sure CPU freq is scaled back if not needed

02:45PM EDT - Throttle back components that aren't needed for perf / workload

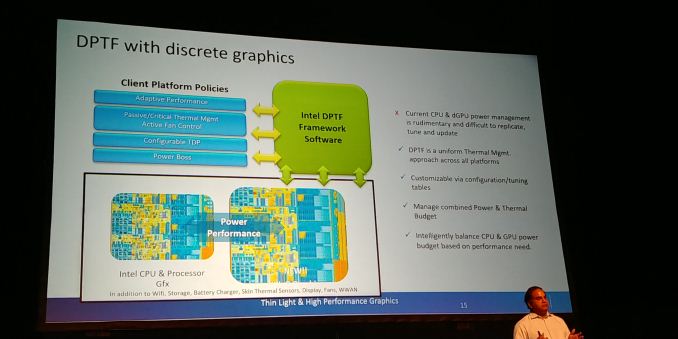

02:45PM EDT - Add discrete GPU like graphics into mix in thin and light

02:45PM EDT - provide hooks in the form of power budget for components to manage

02:46PM EDT - power policies can be used with the control mechanisms in the platform

02:46PM EDT - No shared interfaces between the parts

02:46PM EDT - Software power management solution

02:46PM EDT - Time constraints in seconds, so software is applicable

02:46PM EDT - 100ms control loop latency

02:47PM EDT - allows turbo similar to Turbo Boost 2.0

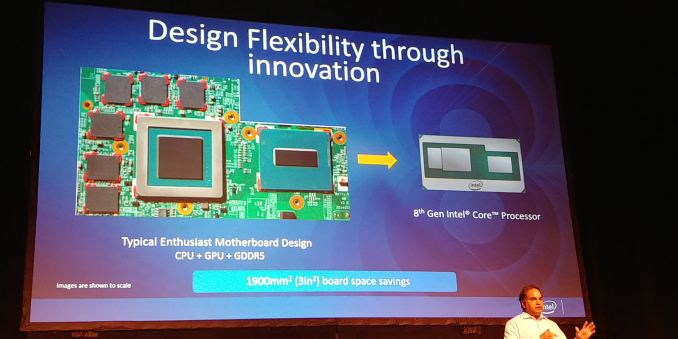

02:47PM EDT - Form factor allows the vendors to physically create thin+light or more performant form factors vs discrete graphics

02:47PM EDT - 4GB of HBM2, 1.7mm z-height

02:48PM EDT - Space savings vs GDDR5

02:49PM EDT - OEMs design for 62.5W SDP if this was traditional

02:49PM EDT - Not utilizing full spectrum of power

02:49PM EDT - No way to transfer power

02:50PM EDT - Now describing FIVR for single chip

02:50PM EDT - For discrete GPU, can't do FIVR

02:50PM EDT - but in a single package, can still power (but not as finely)

02:50PM EDT - Similar power sharing power methodology to FIVR at high level

02:50PM EDT - Up to the OEM to determine how to harness the capabilities

02:51PM EDT - design to a power, let the power sharing manage the rest

02:51PM EDT - Compare 15W i7-U plus GTX 1060 with 45W Kaby G with 55-65W Radeon

02:52PM EDT - New design allows Intel be more creative

02:52PM EDT - Faster time to market window

02:52PM EDT - From time made to decision to product was effectively 4.5 quarters

02:53PM EDT - Taking proven silicon and putting them together

02:53PM EDT - Had 90% perf on first boot, rest of tuning

02:53PM EDT - EMIB provides a path to higher bandwidth at lower pwoer

02:54PM EDT - Q&A Time

02:55PM EDT - Q: Have EMIB for HBM to GPU, but no EMIB from CPU to GPU?

02:55PM EDT - A: We use PCIe - doesn't need the density of EMIB for signalling, but you need it for HBM

02:56PM EDT - Q: GPU is Custom?

02:56PM EDT - A: We customized how the HBM interfaced with EMIB

02:57PM EDT - Q: EMIB for heterogeneous - only showing core to HBM. What's the plan for Core to Accelerator ?

02:58PM EDT - A: EMIB is technology - need to create a standardized ecosystem. Intel is actively working on this with DARPA Open Chips. But ecosystem requires a village, not one vendor. We're showing the potential, needs more players

02:59PM EDT - Q: Learned about integration - any more insights into same die ? A: Depends on wires being pulled out. High bandwidth is better on chip, need to evaluate ROI on power.

OK that's a wrap. Our next talk is AMD: https://www.anandtech.com/show/13243