Original Link: https://www.anandtech.com/show/1150

Intel Developer Forum Fall 2003 - Day 1: Gearing up for Prescott

by Anand Lal Shimpi on September 16, 2003 4:55 PM EST- Posted in

- IT Computing

Intel just finished updating us on their 90nm process, which will be used in the production of the first Prescott cores at the end of this year. We've mentioned Prescott quite a bit in the past, so be sure to read our previous IDF coverage on the CPU to get an idea of what it brings to the table.

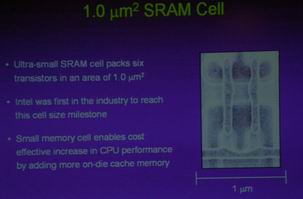

Being Intel's first 90nm CPU as well as using Intel's new ultra-small SRAM cells, allows Prescott to come fully equipped with a 1MB on-die L2 cache. Having such a large cache will be necessary in order to compete with the Athlon 64's on-die memory controller.

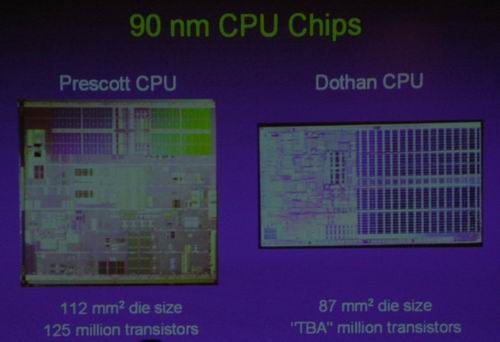

Intel did release some details about the Prescott core, indicating that it will have a 112mm^2 die size (smaller than the 136mm^2 Northwood core), despite having 1MB L2 cache and a total of 125 million transistors (55 million transistors). The majority of the increase in transistors is obviously due to the increase in L2 cache, although there are also some other improvements made to the core that we've explained in the past.

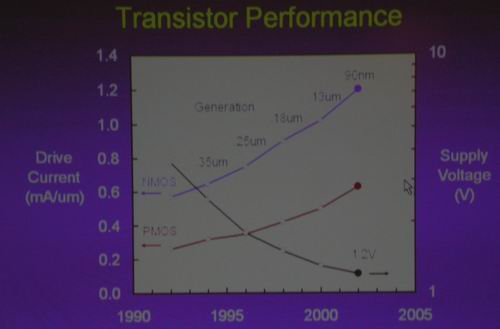

The transistors should run at a voltage of 1.2V, according to this voltage scaling chart:

Intel also revealed a bit about Dothan, the 90nm follow-on to Banias (Pentium-M). Although they didn't reveal transistor counts, Intel did say that Dothan would feature an 87mm^2 die, which is quite small considering its 2MB L2 cache.

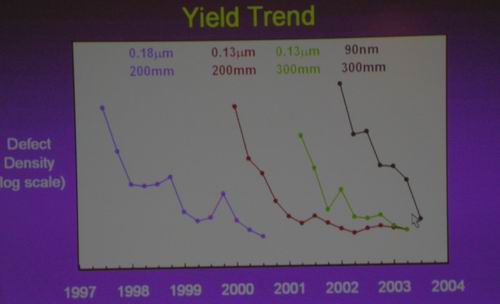

Skeptics of the move to Intel's 90nm process were put to rest as Intel showed data supporting their 90nm process having the quickest reduction in defects in Intel history:

Intel ended the briefing by mentioning that their yields were high enough for mass production, which are fairly high given Intel's standards, although obviously the exact yields weren't disclosed.

Now it's off to Louis Burns' keynote about the "Digital Home"...