Original Link: https://www.anandtech.com/show/11337/samsung-and-tsmc-roadmaps-12-nm-8-nm-and-6-nm-added

Samsung and TSMC Roadmaps: 8 and 6 nm Added, Looking at 22ULP and 12FFC

by Anton Shilov on May 5, 2017 9:30 AM ESTSamsung and TSMC made several important announcements about the present and future of their semiconductor manufacturing technologies in March. Samsung revealed that it had shipped over 70 thousand wafers processed using its first-generation 10 nm FinFET fabrication process (10LPE) and also announced major additions to its upcoming manufacturing technology roadmap. In particular, the company plans to introduce three processes it has not talked about thus far. TSMC said that it is about to start mass production of ICs (integrated circuits) using its first-gen 10 nm technology and also announced several new processes that will be launched in the coming years, including its first 7 nm EUV process due in 2019.

10 nm: Samsung Is Shipping

Update 5/12: Samsung informed us that its press release from October, 2016, compares characteristics of the 10LPE manufacturing technology with those of the 14LPE, not 14LPP. The text and table have been updated accordingly.

Samsung said it had started to make SoCs using its 10LPE fabrication technology last October, which is something we already knew. This manufacturing process allowed the company to make its chips 30% smaller compared to ICs made using its 14LPE process as well as reducing power consumption by 40% (at the same frequency and complexity) or increase their frequency by 27% (at the same power and complexity). So far, Samsung has processed over 70 thousand wafers using its 10LPE technology, which can give an idea about Samsung’s 10 nm production capacities (considering that the whole 10 nm production cycle is greater than the 90 days we saw with previous-gen FinFET processes). At the same time, keep in mind that Samsung does not have many 10 nm designs to manufacture right now: we know only of the company’s own Exynos 9 Octa 8895 as well as Qualcomm’s Snapdragon 835 seen in the Samsung Galaxy S8.

| Advertised PPA Improvements of New Process Technologies Data announced by companies during conference calls, press briefings and in press releases |

||||||||

| GF | Samsung | |||||||

| 7nm DUV vs 14LPP |

14LPP vs 28LPP |

10LPE vs 14LPE |

10LPE vs 14LPP |

10LPP vs 10LPE |

10LPU vs 10LPE |

|||

| Power | >60% | 60% | 40% | 30% | ~15% | ? | ||

| Performance | >30% | 40% | 27% | >10% | ~10% | ? | ||

| Area Reduction | >50% | 50% | 30% | 30% | none | ? | ||

In addition to its production milestone, Samsung also confirmed plans to start mass production of chips using its second-generation 10 nm manufacturing process called 10LPP (10 nm low-power plus) by the end of 2017 as well as its third-generation 10 nm technology called 10LPU by the end of 2018. Samsung said last year that the 10LPP is going to enable a ~10% performance increase (at the same power and at the same complexity) versus the 10LPE, but we know absolutely nothing about the 10LPU. It is logical to assume that the 10LPU will bring certain PPA-related (performance, power, area) improvements, but it is not clear how Samsung plans to achieve them and which one of the three will be the focus for improvements. As it appears, just like Intel, Samsung has ended up with three generations of 14 nm fabrication processes and is going to end up with three generations of 10 nm manufacturing technologies. It is noteworthy that Samsung itself does not use its 14LPC (low-power compact) for its leading edge SoCs, which may suggest that the 10LPU is also not aimed at this segment of the market. In fact, it is highly likely that the 10LPU will target ultra-small and ultra-low-power ICs for various emerging devices, but Samsung yet has to confirm that.

10nm: TSMC Is Steady

As for TSMC, its 10 nm process technology (CLN10FF) is now qualified for production at the company’s GigaFabs 12 and 15, where high-volume ramp is expected to start in H2 2017. Production capacity of these two fabs is hundreds of thousands wafer starts per quarter and TSMC plans to ship 400 thousand wafers processed using its 10 nm manufacturing tech this year. Considering the long production cycles for FinFET-based technologies, it is about time for TSMC to start ramping up 10 nm so to be able to supply enough chips to its main customer in time. Apple is expected to launch its new iPhone products in September or October and needs to get SoCs couple of months before the launch.

| Advertised PPA Improvements of New Process Technologies Data announced by companies during conference calls, press briefings and in press releases |

|||||||

| TSMC | |||||||

| 16FF+ vs 28HPM |

16FF+ vs 20SOC |

10FF vs 16FF+ |

7FF vs 16FF+ |

7FF vs 10FF |

|||

| Power | 70% | 60% | 40% | 60% | <40% | ||

| Performance | 65% | 40% | 20% | 30% | ? | ||

| Area Reduction | ~50% | none | >50% | 70% | >37% | ||

PPA advantages of TSMC’s CLN10FF over its CLN16FF+ (second-gen 16 nm) have been discussed already and they are significant for developers of mobile SoCs (but not that significant for makers of other ICs): a ~50% higher transistor density, a 20% performance improvement at the same power and complexity or a 40% lower power consumption at the same frequency and complexity. Unlike Samsung, TSMC does not seem to plan multiple generations of 10 nm and will go straight to 7 nm next year. 7nm is currently very popular among chip designers, indicating a future major milestone. However, in addition to the CLN7FF, the company will also offer several other manufacturing technologies for ultra-small and ultra-low-power applications.

Beyond 10 nm at TSMC: 7 nm DUV and 7 nm EUV

As noted previously, TSMC’s 7 nm node will be used by tens of companies for hundreds of chips targeting different applications. Initially, the company plans to offer two versions of the manufacturing technology: one for high-performance, and one for mobile applications, both of which will use immersion lithography and DUV. Moreover, eventually TSMC intends to introduce a more advanced 7nm fabrication process that will use EUV for critical layers, taking a page from GlobalFoundries’ book (which is set tp start 7 nm with DUV and then introduces second-gen 7 nm with EUV).

TSMC’s first-generation CLN7FF will enter risk production in Q2 2017 and will be used for over a dozen of tape outs this year. It is expected that high-volume manufacturing (HVM) using the CLN7FF will commence in ~Q2 2018, so, the first “7-nm” ICs will show up in commercial products in the second half of next year. When compared to the CLN16FF+, the CLN7FF will enable chip developers to shrink their die sizes by 70% (at the same transistor count), drop power consumption by 60% or increase frequency by 30% (at the same complexity).

The second-generation 7 nm from TSMC (CLN7FF+) will use EUV for select layers and will require developers to redesign EUV layers according to more aggressive rules. The improved routing density is expected to provide ~10-15-20% area reduction and enable higher performance and/or lower power consumption. In addition, production cycle of such chips will get shorter when compared to ICs made entirely using DUV tools. TSMC plans to start risk production of products using its CLN7FF+ in Q2 2018 and therefore expect HVM to begin in H2 2019.

| Advertised PPA Improvements of TSMC's CLN7FF Nodes Data announced by TSMC during conference calls, press briefings and in press releases |

||||||

| 7FF vs 16FF+ |

7FF vs 10FF |

7FF EUV vs 7FF |

5FF EUV vs 7FF EUV |

|||

| Power | 60% | <40% | 10% | lower | ||

| Performance | 30% | ? | lower | higher | ||

| Area Reduction | 70% | >37% | ~10-15-20% | tangible | ||

| HVM Start | ~Q2 2018 | - | ~H2 2019 | ~H2 2020 | ||

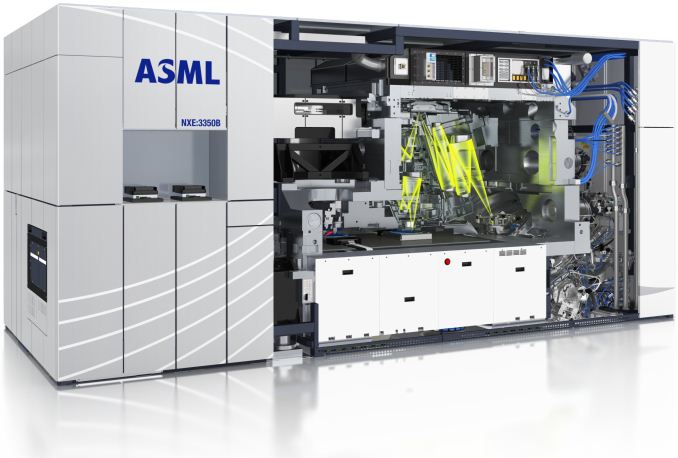

As it turns out, all three leading foundries (GlobalFoundries, Samsung Foundry and TSMC) all intend to start using EUV for select layers with their 7 nm nodes. While ASML and other EUV vendors need to solve a number of issues with the technology, it looks like it will be two years down the road before it will be used for commercial ICs. Of course, certain slips are possible, but looks like 2019 will be the year when EUV will be here. In fact, keeping in mind that both TSMC and Samsung are already talking about their second-gen EUV technologies (which they call 5 and 6 nm) that will use more EUV layers, it looks like the foundries are confident of the ASML TwinScan NXE manufacturing tools (as well as of the Cymer light source, pellicles, photoresists, etc.) they are going to use.

Beyond 10 nm at Samsung: 8 nm and 6 nm

Samsung’s 7 nm manufacturing technology is still expected to be the company’s first process to use extreme ultraviolet lithography (EUVL) for high-volume manufacturing (HVM) and that is going to happen sometimes in 2019 or later (risk production starts in the second half of 2018). In fact, the next several years down the road is where things will start to get interesting as Samsung announced another two new production technologies it has not talked about before: the 8 nm and the 6 nm processes.

| Industry FinFET Lithography Roadmap, HVM Start Data announced by companies during conference calls, press briefings and in press releases |

||||||||||||

| 2016 | 2017 | 2018 | 2019 | 2020 | 2021 | |||||||

| 1H | 2H | 1H | 2H | 1H | 2H | 1H | 2H | |||||

| GlobalFoundries | 14LPP | 7nm DUV | 7nm with EUV* | |||||||||

| Intel | 14 nm 14 nm+ |

14 nm++ 10 nm |

10 nm+ 10 nm++ |

|||||||||

| Samsung | 14LPP 14LPC |

10LPE | 10LPP | 8LPP 10LPU |

7LPP | 6 nm* (?) | ||||||

| SMIC | 28 nm** | 14 nm in development | ||||||||||

| TSMC | CLN16FF+ CLN16FFC | CLN10FF CLN16FFC |

CLN7FF CLN12FFC |

CLN12FFC/ CLN12ULP |

CLN7FF+ | 5 nm* (?) | ||||||

| UMC | 28 nm** | 14nm | no data | |||||||||

| *Exact timing not announced **Planar |

||||||||||||

Officially, Samsung says that both technologies will offer “greater scalability, performance and power advantages when compared to existing process nodes,” which obviously means that they are across the board better than Samsung’s current-gen 14 nm and 10 nm offerings. What is important is that Samsung also says that the “8 nm and the 6 nm will inherit all innovations from the latest 10 nm and the 7 nm technologies” respectively. This means that the 8 nm is set to keep using DUV and multi patterning (triple patterning or even quad patterning to be exact, but Samsung has not confirmed usage of the latter) for critical layers, whereas the 6 nm will come after 7 nm and will be Samsung’s second-generation EUV technology.

The only thing that Samsung confirms about its 8LPP manufacturing technology right now is the fact that this is a DUV-based process technology designed to shrink die size (i.e., increase transistor density) and frequency compared to the 10LPP fabrication process. Given the name of the technology and its key advertised advantages over direct predecessor, it is highly likely that the 8LPP will be used to make high-performance SoCs in 2019.

Since Samsung plans to start risk production using the 7LPP in the second half of 2018, the technology is hardly going to be used for high-volume manufacturing before the second half of 2019. Keeping in mind that Samsung now begins HVM using its leading-edge process technologies in October, it is possible that it is going to kick-off 7LPP HVM in fall 2019, but the 8LPP will be Samsung’s most advanced process technology for the better part of the year. Samsung does not mention timeframes for its 6 nm process technology and what to expect from it, but it is logical to assume that it will require more layers to be processed using ASML's EUV tools (like the NXE:3350B pictured above) in a bid to provide PPA advantages and it not be used for high-volume manufacturing before late 2020.

In March, Samsung only made brief announcements regarding its 10LPU, 8LPP and 6 nm process technology without disclosing their exact specifications or even PPA improvements targets. The addition of at least two more DUV technologies (the 10LPU and the 8LPP) in general may indicate that EUV may not be the best choice for all applications in 2019 – 2021, which is perfectly logical. Then again, we do not know how DUV and EUV technologies will co-exist early in the EUV era.

We are going to learn more about Samsung’s plans in the foundry industry in late May, when the company hosts its 2017 U.S Samsung Foundry Forum. So, we will have to wait for a couple of months for Samsung to disclose the whole picture regarding its upcoming process technologies.

Not Everyone Needs Leading Edge: TSMC’s 22 nm ULP, 12 nm FFC and 12 nm FFC+

Now let’s discuss something less advanced, but what is required for hundreds of millions of devices sold every year.

| Advertised PPA Improvements of TSMC's Low-Power/Compact Nodes Data announced by TSMC during conference calls, press briefings and in press releases |

||||||||

| CLN28HPC vs CLN28HPM |

CLN28HPC+ vs CLN28HPM |

CLN22LPU vs CLNHPC+ |

CLN16FFC vs CLN16FF |

CLN12FFC vs CLN16FFC |

12FFC-ULP vs CLN12FFC |

|||

| Power | 20% | 30% | 35% | lower | 25% | lower | ||

| Performance | - | 15% | 15% | unknown | 10% | unknown | ||

| Area Reduction | 10% | 10% | 10% | optional | 20% | unknown | ||

| HVM Start | started | started | 2018 | Q1 2016 | 2018 | 2019 | ||

| Note | Planar 28 nm-based |

FinFET 16/20 nm-based |

||||||

Development of FinFET-based chips is more expensive of ICs featuring planar transistors and their manufacturing is more costly as well. As a result, FinFET is virtually unavailable for many smaller designers of SoCs that usually build various solutions for emerging IoT applications. GlobalFoundries and Samsung offer their FD-SOI manufacturing processes to such companies (and these technologies have a number of other advantages in addition to being more cost-effective), whereas TSMC intends to introduce its new 22 nm ULP technology aimed at such applications. The CLN22ULP is an optimized version of the company’s 28 nm HPC+ (high-performance compact plus) manufacturing process that has been available for a while. The 22ULP offers a 10% area reduction and either a 15% performance improvement over the 28HPC+ process, or a 35% power drop. The 22ULP process joins a family of other ultra-low-power processes offered by TSMC and will compete against GlobalFoundries 22FDX as well as Samsung’s 28 nm FD-SOI offering.

Next up is TSMC’s 12 nm FFC manufacturing technology, which is an optimized version of the company’s CLN16FFC that is set to use 6T libraries (as opposed to 7.5T and 9T libraries) providing a 20% area reduction. Despite noticeably higher transistor density, the CLN12FFC is expected to also offer a 10% frequency improvement at the same power and complexity or a 25% power reduction at the same clock rate and complexity. Further down the road, TSMC also plans to offer a ULP version of the CLN12FFC with reduced voltage, but that is going to happen only in 2018 or 2019.

Sources: Samsung, TSMC, SemiWiki (1, 2, 3).

Related Reading:

- Samsung Foundry Announces 10nm SoC In Mass-Production

- Samsung Announces Second-Gen 14nm Low Power Plus (14LPP) Process Now In Mass Production

- EUV Lithography Makes Good Progress, Still Not Ready for Prime Time

- GlobalFoundries to Expand Capacities, Build a Fab in China

- Intel to Equip Fab 42 for 7 nm

- GlobalFoundries Updates Roadmap: 7 nm in 2H 2018, EUV Sooner Than Later?