Original Link: https://www.anandtech.com/show/1073

Intel Developer Forum Spring 2003 - Day 2: Prescott Info Galore

by Anand Lal Shimpi on February 19, 2003 1:56 PM EST- Posted in

- Trade Shows

One of the most important tracks to attend at IDF was one about IA32 Architecture Trends and Research, not only because it provides an insight into Intel's plans for upholding Moore's law for the next decade, but also because of a little gem called Prescott.

Intel's Prescott core will be their first CPU built on their new 90nm process, and is due out before the end of this year. We've talked about Prescott for a while, but Intel has finally disclosed all of the major pieces of information about the successor to the Northwood Pentium 4.

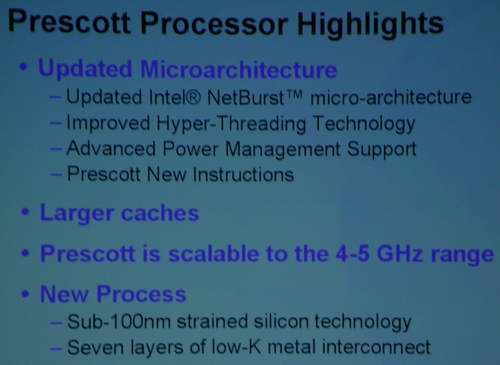

The slide above gives you an idea of the overall improvements to the Prescott core. The updated Intel NetBurst micro-architecture comes in the form of an 800MHz FSB and a larger L1 data cache of 16KB, up from the 8KB of the Willamette and Northwood cores.

The improved Hyper-Threading technology in Prescott comes in the form of two new Hyper-Threading specific instructions, that are a part of the 13 total new instructions that made it into Prescott.

We've been mentioning for a while that Prescott will feature a large 1MB L2 cache, and Intel has publicly confirmed this at IDF. The 1MB L2 cache will bring Prescott up to around 100 million transistors, rivaling some of the most complex GPUs in transistor count.

The 90nm process combined with additional enhancements to Intel's manufacturing processes will allow the Prescott core to scale to the 4 - 5GHz range before it will be replaced by Tejas, which we mentioned earlier today.

The 90nm strained silicon process is something we've talked about in the past, so be sure to check out our previous article on strained silicon to understand the benefits of the technology.

Prescott's Enhancements (continued)

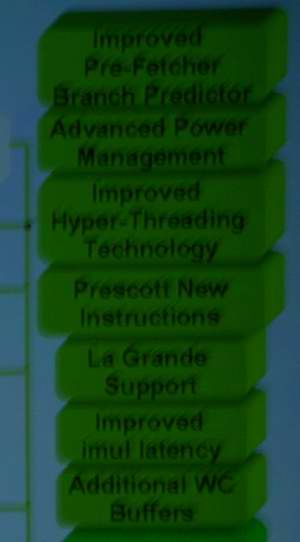

Intel provided a slide diagramming the enhancements to the Prescott core, which is what you'll find below:

The Prescott core does feature an improved pre-fetching algorithm, which helps avoid extremely costly pipeline stalls that can wreak havoc on the deeply pipelined Pentium 4 core.

Intel did mention advanced power management with Prescott, but has yet to disclose exactly what they mean by that. We'll be touching on the improved HT and Prescott New Instructions in the next page, so we'll leave them out of discussion here. With Prescott, Intel will also be introducing LaGrande Support, which is something Intel has talked about at a very high level in the past as a hardware level security standard.

The Prescott core will also have reduced latency on integer multiplies, although we're not told exactly how much of an improvement at this point. And finally there are additional write combining buffers within the core itself.

Prescott New Instructions & Hyper-Threading Improvements

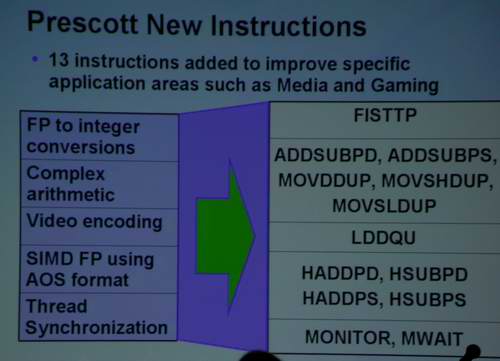

As we mentioned before, the Prescott core features 13 new instructions which are listed below:

As you can see, there are a number of complex arithmetic instructions that can be used in scientific and engineering applications. There isn't much information on the instructions available as of yet, but we'll be working today and tomorrow to get as much information as possible about them.

The two thread synchronization instructions are responsible for improvements in Hyper-Threading performance as they help reduce the collision of threads within the processor itself. Once again, we'll be looking to get more information from Intel as they make it available, so be sure to check back later as we do get more...