Original Link: https://www.anandtech.com/show/15231/western-digital-rollsout-two-new-swerv-riscv-cores

Western Digital Rolls-Out Two New SweRV RISC-V Cores For Microcontrollers

by Anton Shilov on December 13, 2019 5:00 PM EST- Posted in

- Storage

- CPUs

- Western Digital

- RISC-V

- SweRV

Western Digital has added two new processor cores — the SweRV Core EH2 and the SweRV Core EL2 — into its SweRV portfolio of microcontroller CPUs. And, keeping in line with past parts, and the company has made their register-transfer level (RTL) design abstraction available to the industry for free. In addition, the company has also introduced the first hardware reference design for OmniXtend cache coherent memory over Ethernet protocol, and transferred management and support of the architecture to Chips Alliance.

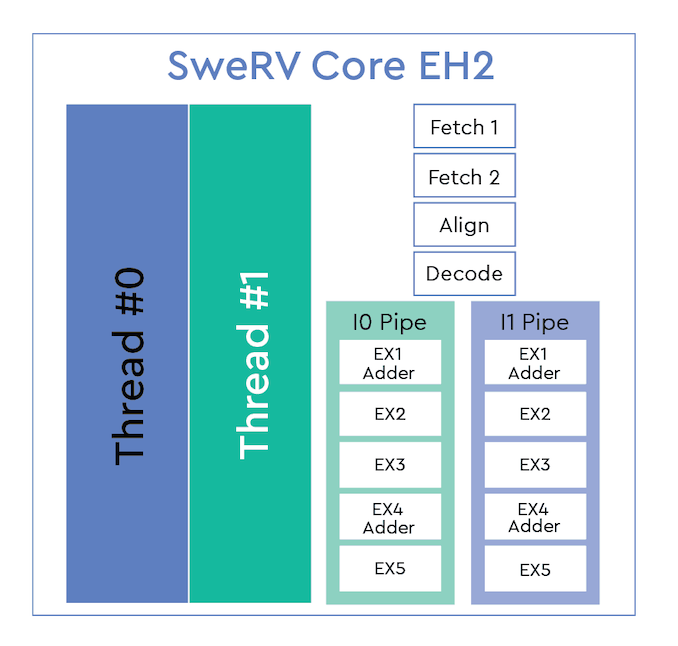

The SweRV Core EH2 is a 32-bit in-order core designed for use in microcontrollers. It uses a 2-way superscalar design with a nine-stage pipeline, and a 2-way simultaneous multithreading capability. In essence, the EH2 is a performance-enhanced version of the EH1 introduced last year that supports SMT and is intended to be made using TSMC’s 16 nm FinFET fabrication technology for maximum PPA (power, performance, area) efficiency. The EH2 core should deliver 6.3 CoreMark/MHz (based on Western Digital’s simulations), up from 4.9 CoreMark/MHz in case of the EH1 and when produced using the said process, it is just 0.067 mm² large (down from 0.11 mm² in case of the EH1 at 28 nm). The SweRV Core EH2 will be used for the same applications as its predecessor (such as SSD controllers), but its enhanced performance and smaller size (at 16 nm) will enable it to address something more complex too.

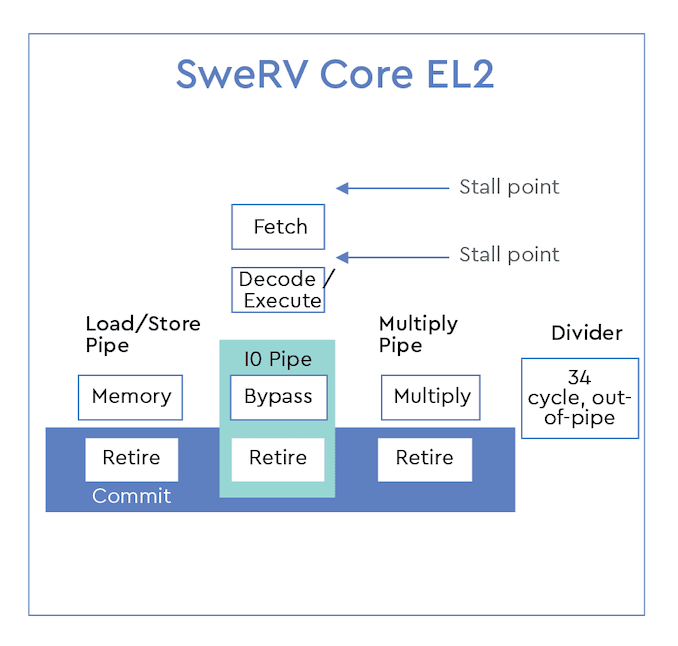

By contrast, the SweRV Core EL2 is all about minimization as it will be used to replace sequential logic and state machines in controller SoCs that have to be as small as possible. The EL2 is a 32-bit in-order core featuring a 1-way scalar design and a four-stage pipeline. Western Digital expects the core to be 0.023 mm² large and deliver performance of around 3.6 CoreMarks/MHz.

| Western Digital's SweRV Cores | |||||||

| Core Name | RISC-V Type |

Pipeline Stages |

Threads | Size @ TSMC |

CoreMark /MHz |

||

| SweRV Core EH1 | RV32IMC | 9-dual issue |

1 | 0.11mm² @ 28nm | 4.9 | ||

| SweRV Core EH2 | 2 | 0.067mm² @ 16 nm | 6.3 | ||||

| SweRV Core EL2 | 4-single issue | 1 | 0.023mm² @ 16 nm | 3.6 | |||

Western Digital says that all of its three SweRV cores will be used in a variety of its products ‘in the near future’, but naturally does not pre-announce them. Meanwhile, contributing these cores to others will enrich the RISC-V ecosystem in general.

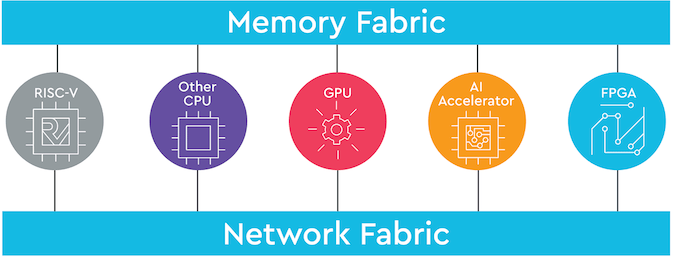

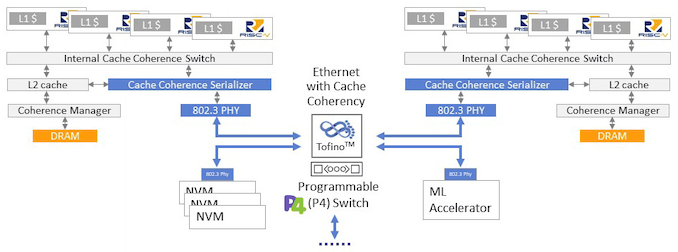

Speaking of the ecosystem, Western Digital presented the first hardware reference design for its OmniXtend cache coherent memory over Ethernet-compatible fabric protocol, enabling developers of chips to implement it into their designs. Initially, the architecture could be used for attaching persistent memory to CPUs, yet it could be integrated into components like GPUs, FPGA, and machine learning accelerators as well. The reference design will be available from Chips Alliance, which will also handle further development of the OmniXtend protocol.

Related Reading:

- Western Digital’s RISC-V "SweRV" Core Design Released For Free

- Western Digital Reveals SweRV RISC-V Core, Cache Coherency over Ethernet Initiative

- Western Digital to Use RISC-V for Controllers, Processors, Purpose-Built Platforms

- Samsung to Use SiFive RISC-V Cores for SoCs, Automotive, 5G Applications

- SiFive Announces First RISC-V OoO CPU Core: The U8-Series Processor IP

Source: Western Digital